业内都知道DUV EUV 光刻的“纳米”是什么游戏

版主: Softfist

#2 Re: 业内都知道DUV EUV 光刻的“纳米”是什么游戏

3nm制程的实际线宽并没有一个固定的物理数值,因为它是一个市场营销和技术指标的名称,而非精确的物理尺寸。这个“3nm”代表的是该芯片制造工艺的先进程度,并且象征着晶体管的性能提升和密度增加,并非指代实际的物理线宽在3纳米。制程技术越先进,在相同面积的芯片上能够集成越多的晶体管,从而提高芯片的性能和效率。

以下是更详细的解释:

市场和技术指标的演变:

芯片制程的命名,例如“3nm”,已经演变成一种行业内的技术标签,用来表示工艺的世代和成熟度,而不是晶体管或导线实际的物理尺寸。

尺寸的相对性:

在实际制造中,晶体管的尺寸会比制程名称小得多,而且可能存在多种不同的尺寸,如门宽、沟道长度等。

提升性能和集成度:

制程技术进步的核心在于能够在有限的芯片面积上集成更多的晶体管,从而提高计算能力、降低功耗并提升效率。

与逻辑密度相关的术语:

早期制程名称可能与某些关键尺寸(如栅极长度)相关,但随着技术的发展,这个数字更多地代表了一种逻辑上的密度指标,与晶体管的整体性能相关,而非单一的线宽值。

以下是更详细的解释:

市场和技术指标的演变:

芯片制程的命名,例如“3nm”,已经演变成一种行业内的技术标签,用来表示工艺的世代和成熟度,而不是晶体管或导线实际的物理尺寸。

尺寸的相对性:

在实际制造中,晶体管的尺寸会比制程名称小得多,而且可能存在多种不同的尺寸,如门宽、沟道长度等。

提升性能和集成度:

制程技术进步的核心在于能够在有限的芯片面积上集成更多的晶体管,从而提高计算能力、降低功耗并提升效率。

与逻辑密度相关的术语:

早期制程名称可能与某些关键尺寸(如栅极长度)相关,但随着技术的发展,这个数字更多地代表了一种逻辑上的密度指标,与晶体管的整体性能相关,而非单一的线宽值。

#3 Re: 业内都知道DUV EUV 光刻的“纳米”是什么游戏

芯片制程背后的秘密:三星、台积电的3nm,实际是22nm?

2022年末,台积电实现了3nm工艺,而在半年之前,三星实现了3nm工艺。

那么问题就来了,3nm工艺究竟代表的是芯片的哪一部分是3nm?估计没有谁能够说清楚,而事实上也是如此,因为与3nm芯片的所有关键指标中,没有一项是3nm。

2022年末,台积电实现了3nm工艺,而在半年之前,三星实现了3nm工艺。

那么问题就来了,3nm工艺究竟代表的是芯片的哪一部分是3nm?估计没有谁能够说清楚,而事实上也是如此,因为与3nm芯片的所有关键指标中,没有一项是3nm。

#4 Re: 业内都知道DUV EUV 光刻的“纳米”是什么游戏

你这个文章标题和内容根本不是一回事,DUV光源是193nm,EUV 13.5nm。这些数据是实打实的。至于芯片上的纳米,那是另外一回事

#5 Re: 业内都知道DUV EUV 光刻的“纳米”是什么游戏

duv euv的到的支撑,几纳米已经成了营销游戏,而不是具体物理线宽和参数

随着芯片工艺的改进,NIL技术将超越“?UV”的搞法 良率高,能耗低,所见即所得。。。。

狗子真是什么都不懂,捏着JJ充六指

随着芯片工艺的改进,NIL技术将超越“?UV”的搞法 良率高,能耗低,所见即所得。。。。

狗子真是什么都不懂,捏着JJ充六指

-

Linjiaojiao

- 著名点评

- 帖子互动: 173

- 帖子: 3283

- 注册时间: 2022年 7月 24日 21:42

-

Linjiaojiao

- 著名点评

- 帖子互动: 173

- 帖子: 3283

- 注册时间: 2022年 7月 24日 21:42

#16 Re: 业内都知道DUV EUV 光刻的“纳米”是什么游戏

22NM指光刻做到22nm 后面由etch的来shrink到3 nmredot 写了: 2025年 8月 12日 16:20 芯片制程背后的秘密:三星、台积电的3nm,实际是22nm?

2022年末,台积电实现了3nm工艺,而在半年之前,三星实现了3nm工艺。

那么问题就来了,3nm工艺究竟代表的是芯片的哪一部分是3nm?估计没有谁能够说清楚,而事实上也是如此,因为与3nm芯片的所有关键指标中,没有一项是3nm。

通常指 gate size

#17 Re: 业内都知道DUV EUV 光刻的“纳米”是什么游戏

Gemini 给答案:

In a 3nm chip, no single part or physical dimension directly measures 3nm. The "3nm" label is primarily a marketing term indicating a generation of technology with improved performance, density, and power efficiency compared to previous nodes (like the 5nm node). While it signifies increased miniaturization and smaller transistors, it doesn't refer to the physical size of the gate, metal pitch, or any other specific feature of the transistor itself, which are much larger.

What "3nm" means for a chip:

A marketing term:

It's used by chip manufacturers to signal a new, improved generation of technology.

Technological advancements:

It represents a higher degree of miniaturization for transistors, leading to:

Increased transistor density.

Higher speed.

Reduced power consumption.

No fixed standard:

There is no industry-wide agreement on what "3nm" specifically defines, so it's often compared to the previous process node from the same manufacturer.

Not the actual transistor size:

The actual physical dimensions of a transistor, such as the gate length or metal pitch, are significantly larger than 3nm. For example, a 3nm node's contacted gate pitch is projected to be around 48nm, and the tightest metal pitch around 24nm.

In a 3nm chip, no single part or physical dimension directly measures 3nm. The "3nm" label is primarily a marketing term indicating a generation of technology with improved performance, density, and power efficiency compared to previous nodes (like the 5nm node). While it signifies increased miniaturization and smaller transistors, it doesn't refer to the physical size of the gate, metal pitch, or any other specific feature of the transistor itself, which are much larger.

What "3nm" means for a chip:

A marketing term:

It's used by chip manufacturers to signal a new, improved generation of technology.

Technological advancements:

It represents a higher degree of miniaturization for transistors, leading to:

Increased transistor density.

Higher speed.

Reduced power consumption.

No fixed standard:

There is no industry-wide agreement on what "3nm" specifically defines, so it's often compared to the previous process node from the same manufacturer.

Not the actual transistor size:

The actual physical dimensions of a transistor, such as the gate length or metal pitch, are significantly larger than 3nm. For example, a 3nm node's contacted gate pitch is projected to be around 48nm, and the tightest metal pitch around 24nm.

#18 Re: 业内都知道DUV EUV 光刻的“纳米”是什么游戏

在3nm芯片中,并没有任何一个物理测量给出3nm这个参数

a 3nm node's contacted gate pitch is projected to be around 48nm, and the tightest metal pitch around 24nm.

In summary: When a manufacturer labels a chip as "3nm," they are indicating a new, more advanced, and more efficient chip based on their own internal process evolution, rather than providing a specific physical dimension within the chip.

a 3nm node's contacted gate pitch is projected to be around 48nm, and the tightest metal pitch around 24nm.

In summary: When a manufacturer labels a chip as "3nm," they are indicating a new, more advanced, and more efficient chip based on their own internal process evolution, rather than providing a specific physical dimension within the chip.

#19 Re: 业内都知道DUV EUV 光刻的“纳米”是什么游戏

In a 3nm chip, the "3nm" designation is a marketing term, not a literal physical measurement of any specific dimension like gate length or metal pitch. It signifies a generation of technology with higher transistor density and better performance compared to previous generations, but there is no universal industry standard for what constitutes a 3nm process node.

Why it's a marketing term:

Historical context:

In the past, the node number was more directly related to the gate length of the transistor.

Loss of physical meaning:

As chip technology evolved, this direct correlation was lost. Manufacturers use the term to indicate improved performance, speed, and power efficiency compared to their own previous processes, such as their 5nm node.

No industry agreement:

There is no industry-wide agreement on what precise physical measurement should define a 3nm node.

What it actually represents:

Technological generation: It refers to the latest generation of technology used to manufacture the chip.

Increased miniaturization: It indicates a higher degree of miniaturization and transistor density.

Improved performance: This generally leads to increased speed and reduced power consumption.

In summary: When a manufacturer labels a chip as "3nm," they are indicating a new, more advanced, and more efficient chip based on their own internal process evolution, rather than providing a specific physical dimension within the chip.

Why it's a marketing term:

Historical context:

In the past, the node number was more directly related to the gate length of the transistor.

Loss of physical meaning:

As chip technology evolved, this direct correlation was lost. Manufacturers use the term to indicate improved performance, speed, and power efficiency compared to their own previous processes, such as their 5nm node.

No industry agreement:

There is no industry-wide agreement on what precise physical measurement should define a 3nm node.

What it actually represents:

Technological generation: It refers to the latest generation of technology used to manufacture the chip.

Increased miniaturization: It indicates a higher degree of miniaturization and transistor density.

Improved performance: This generally leads to increased speed and reduced power consumption.

In summary: When a manufacturer labels a chip as "3nm," they are indicating a new, more advanced, and more efficient chip based on their own internal process evolution, rather than providing a specific physical dimension within the chip.

#20 Re: 业内都知道DUV EUV 光刻的“纳米”是什么游戏

格家AI斗个法?

GPT-4.1 nano

In a 3nm chip, the term “3nm” primarily refers to a technological node or process node, which historically related to the smallest transistor features or feature sizes. However, in modern semiconductor manufacturing, it does not correspond to a single physical dimension but rather to a set of advanced manufacturing techniques and design rules.

Which physical dimension corresponds to the “3nm” label?

Typically not a single physical dimension:

Unlike earlier process nodes where “22nm” or “14nm” referenced specific physical feature sizes, the “3nm” designation is more of a marketing and technological milestone indicating a new generation of chip fabrication process capabilities.

Physical features are smaller than 3nm:

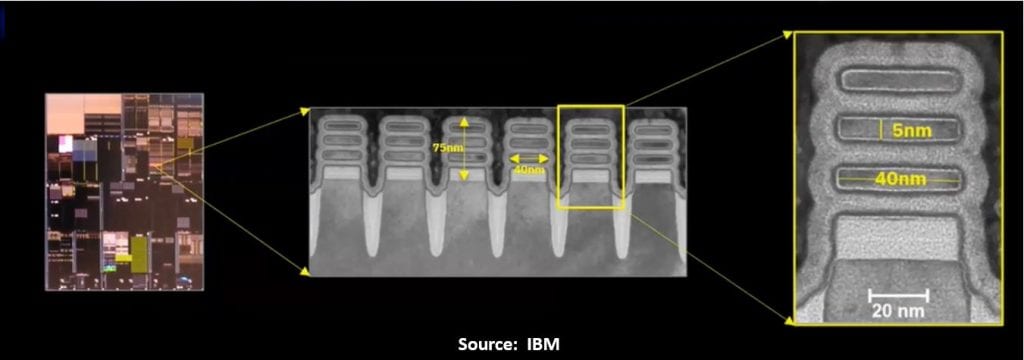

The smallest features, such as transistor gate lengths, are actually smaller than 3nm. For instance, transistor gate lengths in a 3nm process might be around 10-15nm or more, depending on the transistor architecture and design rules.

Measurable critical dimensions:

The actual physical measurements that might approach or be smaller than 3nm include:

Gate lengths (the length of the transistor’s gate electrode)

Fin widths in FinFET transistors

Spacer widths and doping regions

But these are lithographically defined features, and their exact sizes depend on design and manufacturing tolerances.

Summary:

The “3nm” designation is a process node label indicating advanced fabrication technology, not the measurement of a single physical dimension.

The physical features (like transistor gate lengths) in a 3nm process are generally larger than 3nm, but feature sizes like gate lengths may be on the order of 10–15nm or smaller, depending on the design.

The actual “3nm” measurement is not a specific physical dimension but rather a milestone in semiconductor manufacturing technology, representing the scaled-down dimensions enabled by new process techniques.

In essence:

The “3nm” term doesn’t specify one particular measured dimension. Instead, it signifies the overall technological process generation, with physical features like transistor gates being scaled down considerably from previous nodes, but not necessarily exactly 3nm in any one dimension.

Gemini-2.5-Flash

This is a fantastic and very common question, and the answer is a bit nuanced because the “3nm” in a 3nm chip is not a direct physical measurement of any single, easily identifiable dimension on the chip anymore.

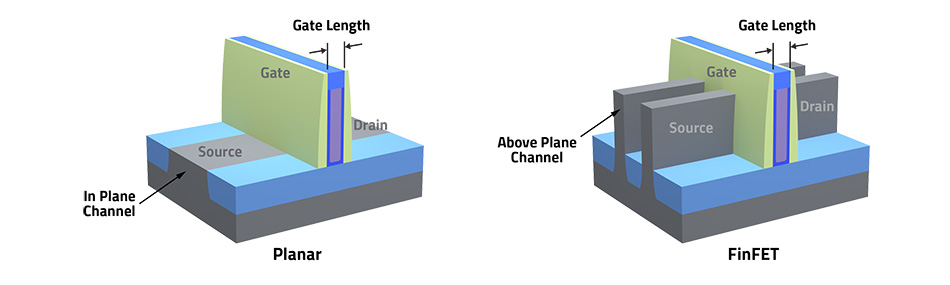

Historically, the process node number (like 90nm, 65nm) used to closely correspond to the transistor gate length. The gate length is a critical dimension that controls the flow of current through the transistor, and making it smaller generally led to faster and more power-efficient transistors.

However, once we got down to around the 22nm/14nm nodes, this correlation broke down significantly. The number became more of a marketing term and an indicator of a new generation of manufacturing technology, signifying a certain level of improvement in:

Transistor Density: How many transistors can be packed into a square millimeter. This is the primary real-world improvement.

Performance: Faster switching speeds.

Power Efficiency: Lower power consumption per transistor.

So, what does physically measure in the single-digit nanometers (including ~3nm) on a 3nm chip?

While not exactly 3nm, the following critical dimensions will be in that incredibly small range:

Gate Pitch (Contacted Gate Pitch - CGP): This is the distance between the center of one transistor gate and the center of the next gate in a repeating pattern. It’s a key determinant of how tightly packed transistors can be. For 3nm, this will be a very small number, likely in the range of 40-50nm, but its components are much smaller.

Metal Pitch (Minimum Metal Pitch - MMP): This is the distance between the center of one metal interconnect line and the center of the next in the lowest metal layers. Smaller metal pitch allows for denser wiring, which is crucial for connecting billions of transistors. This is also a key density driver, with values likely in the 20-30nm range for 3nm.

Fin Width / Nanosheet Thickness (for GAAFETs):

FinFETs: For older nodes (like 7nm, 5nm), transistors are often FinFETs (Fin Field-Effect Transistors), where the current flows over a 3D “fin.” The width of these fins is a critical dimension and would be in the very low single-digit nanometers.

GAAFETs (Gate-All-Around FETs) / Nanosheet Transistors: The 3nm node is expected to be one of the first widespread nodes to use Gate-All-Around (GAA) transistors, often implemented as “nanosheet” or “nanowire” transistors. Instead of a fin, the current flows through horizontal sheets (or vertical wires) of silicon. The thickness (and width) of these individual silicon nanosheets/nanowires will be a key dimension, and these can indeed be in the very low single-digit nanometer range (e.g., 5nm, or even less for some designs). These are the actual channels where electrons flow. The stack of these nanosheets would be taller, but the individual sheet thickness is incredibly tiny.

Gate Length (Actual Physical Gate Length): While not the defining 3nm number, the actual physical gate length of the transistors will also be incredibly small, likely in the range of 10-15nm or even less for performance-optimized transistors. It’s still a critical dimension, but no longer matches the node name.

In summary:

When you hear “3nm chip,” think of it as a significant generational leap in manufacturing technology that allows for:

Vastly increased transistor density: Billions more transistors in the same area.

Improved performance and power efficiency.

Miniaturization of various critical features (like nanosheet thickness, fin width, gate length, and especially the pitches between repeating structures like gates and metal lines) into the single-digit nanometer range.

So, while no single part on a 3nm chip is exactly 3nm, the overall scale of the smallest, most critical features (especially the dimensions of the transistor channel like nanosheet thickness) is indeed operating at that incredibly tiny scale.

GPT-5-nano

Short answer: there isn’t a single physical dimension on a 3 nm chip that is exactly 3 nm. The “3 nm” label is a node name for the generation of technology, not a one-to-one measurement of a specific feature.

More detail:

In modern nodes (including 3 nm), the 3 nm designation mainly signals higher transistor density and better performance, achieved with new device concepts (e.g., gate-all-around nanosheet or nanowire FETs) and more advanced patterning. It does not correspond to a specific feature length you can measure with a ruler.

Actual feature sizes are still well above 3 nm for most lithography-created features. The smallest physical dimensions you’d typically talk about are in the tens of nanometers for things like gate length, interconnect pitch, and contact sizes.

The closest thing to a “3 nm scale” that might be used in the design is the thickness of the nanosheet/channel in GAAFET devices, which can be a few nanometers and is indeed a target in process development. But this is vendor-specific and not universal across all 3 nm designs.

Bottom line: 3 nm describes the technology generation (density, performance, and process capability) rather than a single, measurable 3 nm dimension on the chip.

DeepSeek-R1-0528

The term “3nm” in semiconductor manufacturing is a marketing and generational label rather than a direct measurement of a specific physical dimension. However, it loosely correlates with key scaled-down features in the transistor design. Here’s a breakdown:

Historical Context: Older process nodes (e.g., 90nm, 65nm) were named after the gate length of planar transistors. As technology advanced, this naming convention became decoupled from actual physical dimensions due to complexity and innovation in transistor design.

Modern Transistors: In FinFET (3D) and Gate-All-Around (GAA) nanosheet transistors (used in 3nm nodes), critical dimensions include:

Fin Width (FinFET): In earlier nodes (e.g., 7nm), fin widths were ~5–7nm. For 3nm, this may shrink further but is not exactly 3nm.

Nanosheet Thickness/Width (GAA): In Samsung’s 3nm GAAFET, nanosheet channels are likely ~3–5nm thick, aligning closer to the node name. This dimension improves electrostatic control and reduces leakage.

Other Metrics:

Contacted Gate Pitch (CGP): The distance between adjacent transistor gates. While not 3nm, it scales with each node (e.g., 54nm for 7nm, smaller for 3nm).

Metal Pitch: Interconnect spacing, also reduced but larger than 3nm.

Density: 3nm primarily denotes increased transistor density (more transistors/mm²) rather than a single feature size.

Lithography: Extreme Ultraviolet (EUV) lithography enables patterning of tiny features, but the 3nm node relies on multi-patterning and EUV enhancements to achieve sub-10nm critical layers.

Conclusion: The “3nm” label reflects generational improvements in density, power, and performance. The closest physical approximation is the nanosheet thickness in GAA transistors (~3–5nm) or similarly scaled fin/gate dimensions, though no single feature is exactly 3nm. The term remains a industry benchmark rather than a literal measurement.

GPT-4.1 nano

In a 3nm chip, the term “3nm” primarily refers to a technological node or process node, which historically related to the smallest transistor features or feature sizes. However, in modern semiconductor manufacturing, it does not correspond to a single physical dimension but rather to a set of advanced manufacturing techniques and design rules.

Which physical dimension corresponds to the “3nm” label?

Typically not a single physical dimension:

Unlike earlier process nodes where “22nm” or “14nm” referenced specific physical feature sizes, the “3nm” designation is more of a marketing and technological milestone indicating a new generation of chip fabrication process capabilities.

Physical features are smaller than 3nm:

The smallest features, such as transistor gate lengths, are actually smaller than 3nm. For instance, transistor gate lengths in a 3nm process might be around 10-15nm or more, depending on the transistor architecture and design rules.

Measurable critical dimensions:

The actual physical measurements that might approach or be smaller than 3nm include:

Gate lengths (the length of the transistor’s gate electrode)

Fin widths in FinFET transistors

Spacer widths and doping regions

But these are lithographically defined features, and their exact sizes depend on design and manufacturing tolerances.

Summary:

The “3nm” designation is a process node label indicating advanced fabrication technology, not the measurement of a single physical dimension.

The physical features (like transistor gate lengths) in a 3nm process are generally larger than 3nm, but feature sizes like gate lengths may be on the order of 10–15nm or smaller, depending on the design.

The actual “3nm” measurement is not a specific physical dimension but rather a milestone in semiconductor manufacturing technology, representing the scaled-down dimensions enabled by new process techniques.

In essence:

The “3nm” term doesn’t specify one particular measured dimension. Instead, it signifies the overall technological process generation, with physical features like transistor gates being scaled down considerably from previous nodes, but not necessarily exactly 3nm in any one dimension.

Gemini-2.5-Flash

This is a fantastic and very common question, and the answer is a bit nuanced because the “3nm” in a 3nm chip is not a direct physical measurement of any single, easily identifiable dimension on the chip anymore.

Historically, the process node number (like 90nm, 65nm) used to closely correspond to the transistor gate length. The gate length is a critical dimension that controls the flow of current through the transistor, and making it smaller generally led to faster and more power-efficient transistors.

However, once we got down to around the 22nm/14nm nodes, this correlation broke down significantly. The number became more of a marketing term and an indicator of a new generation of manufacturing technology, signifying a certain level of improvement in:

Transistor Density: How many transistors can be packed into a square millimeter. This is the primary real-world improvement.

Performance: Faster switching speeds.

Power Efficiency: Lower power consumption per transistor.

So, what does physically measure in the single-digit nanometers (including ~3nm) on a 3nm chip?

While not exactly 3nm, the following critical dimensions will be in that incredibly small range:

Gate Pitch (Contacted Gate Pitch - CGP): This is the distance between the center of one transistor gate and the center of the next gate in a repeating pattern. It’s a key determinant of how tightly packed transistors can be. For 3nm, this will be a very small number, likely in the range of 40-50nm, but its components are much smaller.

Metal Pitch (Minimum Metal Pitch - MMP): This is the distance between the center of one metal interconnect line and the center of the next in the lowest metal layers. Smaller metal pitch allows for denser wiring, which is crucial for connecting billions of transistors. This is also a key density driver, with values likely in the 20-30nm range for 3nm.

Fin Width / Nanosheet Thickness (for GAAFETs):

FinFETs: For older nodes (like 7nm, 5nm), transistors are often FinFETs (Fin Field-Effect Transistors), where the current flows over a 3D “fin.” The width of these fins is a critical dimension and would be in the very low single-digit nanometers.

GAAFETs (Gate-All-Around FETs) / Nanosheet Transistors: The 3nm node is expected to be one of the first widespread nodes to use Gate-All-Around (GAA) transistors, often implemented as “nanosheet” or “nanowire” transistors. Instead of a fin, the current flows through horizontal sheets (or vertical wires) of silicon. The thickness (and width) of these individual silicon nanosheets/nanowires will be a key dimension, and these can indeed be in the very low single-digit nanometer range (e.g., 5nm, or even less for some designs). These are the actual channels where electrons flow. The stack of these nanosheets would be taller, but the individual sheet thickness is incredibly tiny.

Gate Length (Actual Physical Gate Length): While not the defining 3nm number, the actual physical gate length of the transistors will also be incredibly small, likely in the range of 10-15nm or even less for performance-optimized transistors. It’s still a critical dimension, but no longer matches the node name.

In summary:

When you hear “3nm chip,” think of it as a significant generational leap in manufacturing technology that allows for:

Vastly increased transistor density: Billions more transistors in the same area.

Improved performance and power efficiency.

Miniaturization of various critical features (like nanosheet thickness, fin width, gate length, and especially the pitches between repeating structures like gates and metal lines) into the single-digit nanometer range.

So, while no single part on a 3nm chip is exactly 3nm, the overall scale of the smallest, most critical features (especially the dimensions of the transistor channel like nanosheet thickness) is indeed operating at that incredibly tiny scale.

GPT-5-nano

Short answer: there isn’t a single physical dimension on a 3 nm chip that is exactly 3 nm. The “3 nm” label is a node name for the generation of technology, not a one-to-one measurement of a specific feature.

More detail:

In modern nodes (including 3 nm), the 3 nm designation mainly signals higher transistor density and better performance, achieved with new device concepts (e.g., gate-all-around nanosheet or nanowire FETs) and more advanced patterning. It does not correspond to a specific feature length you can measure with a ruler.

Actual feature sizes are still well above 3 nm for most lithography-created features. The smallest physical dimensions you’d typically talk about are in the tens of nanometers for things like gate length, interconnect pitch, and contact sizes.

The closest thing to a “3 nm scale” that might be used in the design is the thickness of the nanosheet/channel in GAAFET devices, which can be a few nanometers and is indeed a target in process development. But this is vendor-specific and not universal across all 3 nm designs.

Bottom line: 3 nm describes the technology generation (density, performance, and process capability) rather than a single, measurable 3 nm dimension on the chip.

DeepSeek-R1-0528

The term “3nm” in semiconductor manufacturing is a marketing and generational label rather than a direct measurement of a specific physical dimension. However, it loosely correlates with key scaled-down features in the transistor design. Here’s a breakdown:

Historical Context: Older process nodes (e.g., 90nm, 65nm) were named after the gate length of planar transistors. As technology advanced, this naming convention became decoupled from actual physical dimensions due to complexity and innovation in transistor design.

Modern Transistors: In FinFET (3D) and Gate-All-Around (GAA) nanosheet transistors (used in 3nm nodes), critical dimensions include:

Fin Width (FinFET): In earlier nodes (e.g., 7nm), fin widths were ~5–7nm. For 3nm, this may shrink further but is not exactly 3nm.

Nanosheet Thickness/Width (GAA): In Samsung’s 3nm GAAFET, nanosheet channels are likely ~3–5nm thick, aligning closer to the node name. This dimension improves electrostatic control and reduces leakage.

Other Metrics:

Contacted Gate Pitch (CGP): The distance between adjacent transistor gates. While not 3nm, it scales with each node (e.g., 54nm for 7nm, smaller for 3nm).

Metal Pitch: Interconnect spacing, also reduced but larger than 3nm.

Density: 3nm primarily denotes increased transistor density (more transistors/mm²) rather than a single feature size.

Lithography: Extreme Ultraviolet (EUV) lithography enables patterning of tiny features, but the 3nm node relies on multi-patterning and EUV enhancements to achieve sub-10nm critical layers.

Conclusion: The “3nm” label reflects generational improvements in density, power, and performance. The closest physical approximation is the nanosheet thickness in GAA transistors (~3–5nm) or similarly scaled fin/gate dimensions, though no single feature is exactly 3nm. The term remains a industry benchmark rather than a literal measurement.

#21 Re: 业内都知道DUV EUV 光刻的“纳米”是什么游戏

GPT-4o mini

In a 3nm chip, the term “3nm” typically refers to the technology node used in semiconductor manufacturing, which is often associated with the smallest half-pitch of contactable features in the chip’s design. However, it’s important to note that “3nm” does not refer to a specific physical dimension of a transistor or any single part of the chip.

In modern semiconductor technology, the 3nm node generally indicates the following:

Transistor Gate Length: The gate length of transistors in a 3nm process is often in the range of a few nanometers, but it may not be exactly 3nm. The actual physical dimensions can vary based on the specific design and technology used.

Fin Width: In FinFET (Fin Field-Effect Transistor) technology, which is commonly used in advanced nodes, the width of the fins (the vertical structures that form the channel of the transistor) may also be around the 3nm mark.

Contact and Interconnect Features: The 3nm designation can also refer to the minimum feature size for various interconnects and other elements on the chip.

Overall Density: The 3nm node indicates a significant increase in transistor density, allowing for more transistors to be packed into a given area, which can lead to improved performance and energy efficiency.

In summary, while “3nm” is a marketing term that signifies a level of technology and capability in semiconductor manufacturing, it does not correspond to a single physical measurement but rather a set of dimensions and characteristics associated with the manufacturing process and the resulting chip design.

豆包 1.5 Pro

In a 3 - nm chip, the “3 nm” originally referred to the gate length of the transistors on the chip, although it has become more of a marketing - and - technology - generation term in modern semiconductor manufacturing. Here’s a detailed explanation:

Traditional meaning: Gate length

Transistor structure and gate role

A transistor is the fundamental building block of a semiconductor chip. It consists of a source, a drain, and a gate. The gate acts as a switch that controls the flow of electrons between the source and the drain. When a voltage is applied to the gate, it allows or blocks the flow of current, enabling the binary operations (0s and 1s) that form the basis of digital computing.

The gate length is the physical distance between the source and the drain, measured along the path of electron flow under the gate. In the early days of semiconductor technology development, the gate length was a crucial parameter directly related to the performance and power consumption of transistors.

Impact of reducing gate length

Reducing the gate length to 3 nm offers several advantages. Shorter gate lengths allow electrons to travel a shorter distance between the source and the drain, which means that transistors can switch on and off more quickly. This results in higher - speed operation of the chip, enabling faster data processing and better overall performance.

Additionally, shorter gate lengths generally lead to lower power consumption. Since the electrons have less distance to travel, less energy is dissipated as heat during the switching process.

Modern interpretation

Beyond gate length

As semiconductor technology has advanced, the relationship between the named “node” (such as 3 nm) and the actual gate length has become less straightforward. Chip manufacturers now use the node number as a way to represent an overall advancement in the manufacturing process, which includes improvements in multiple aspects such as transistor architecture, materials, and patterning techniques.

For example, modern chips may use fin - field - effect transistors (FinFETs) or even more advanced transistor structures like gate - all - around (GAA) transistors. In these complex architectures, the 3 - nm designation encompasses improvements in the overall density of transistors on the chip, power efficiency, and performance, rather than simply referring to the gate length. The actual gate length may be different from 3 nm, but the overall technology generation is still labeled as 3 nm to signify its advanced nature compared to previous nodes.

浮点搜索2.0

思考了 7 秒

3nm芯片中,“3nm”这个数值并非指任何单个物理部件的精确尺寸。它是一个工艺节点的标识符,代表着芯片制造技术的进步,反映了芯片整体密度、功耗和性能的提升,而非某个特定物理尺寸[1, 3, 6]。

虽然一些资料提到3nm可能对应着晶体管中某个最小尺寸的物理特征[2, 9, 10],例如栅极长度或金属间距,但实际上并没有一个单一的、普遍接受的定义3。 不同厂商的3nm工艺,其具体的物理尺寸(例如鳍式场效应晶体管FinFET的鳍片宽度、接触多晶硅间距CPP、金属间距等)都可能有所不同[4, 5, 9]。 例如,一个所谓的“7nm”晶体管的实际尺寸可能远大于7nm,例如57x40nm4。 而且,随着技术的进步,用于衡量芯片尺寸的指标也在不断变化10。

总而言之,3nm更像是一个营销术语,代表着比前代工艺更先进的制造技术,而不是某个特定物理部件的精确尺寸1。 要精确测量3nm芯片的各个部件尺寸,需要用到诸如CD-SEM(关键尺寸扫描电子显微镜)、原子力显微镜(AFM)、透射电子显微镜(TEM)等先进的纳米级测量设备[11, 12, 15, 18],并且测量结果会因测量方法和具体部件而异。 目前,即使是最先进的测量技术,也难以达到1nm以下的精度[11, 13]。

DeepSeek-R1满血版

思考了 23 秒

In a 3nm chip process, the term “3nm” does not correspond to a specific physical dimension of any single component. Instead, it is a marketing and generational label inherited from historical naming conventions, reflecting incremental improvements in transistor density, power efficiency, and performance over previous nodes (e.g., 5nm, 7nm). Here’s a breakdown of key points:

Historical Context:

Older nodes (e.g., 90nm, 65nm) were named after the gate length (the distance between a transistor’s source and drain). This metric directly influenced performance and power.

As transistors shrank below ~30nm, the naming convention diverged from literal measurements due to complex 3D designs (e.g., FinFETs) and marketing strategies.

Modern Transistor Structures:

In FinFET or GAAFET (Gate-All-Around) transistors, features like fin width, gate length, and metal pitch are critical but not directly tied to the “3nm” label.

For example, in a 3nm node:

Gate length might be ~12–14nm (far larger than 3nm).

Fin pitch or metal interconnect pitch could be ~20–30nm.

These dimensions are scaled down from previous nodes but remain larger than the process name suggests.

Industry Dynamics:

The lack of standardization allows companies (TSMC, Samsung, Intel) to use the “3nm” label flexibly, often for competitive positioning. One foundry’s “3nm” might match another’s “5nm” in density or performance.

Advancements like EUV lithography enable finer patterning but do not anchor the node name to a specific feature.

Key Takeaway:

The “3nm” designation signifies generational progress rather than a measurable 3nm component. It reflects overall improvements in transistor density (e.g., more transistors per mm²), power efficiency, and speed compared to earlier nodes, even though no individual feature is exactly 3nm.

In a 3nm chip, the term “3nm” typically refers to the technology node used in semiconductor manufacturing, which is often associated with the smallest half-pitch of contactable features in the chip’s design. However, it’s important to note that “3nm” does not refer to a specific physical dimension of a transistor or any single part of the chip.

In modern semiconductor technology, the 3nm node generally indicates the following:

Transistor Gate Length: The gate length of transistors in a 3nm process is often in the range of a few nanometers, but it may not be exactly 3nm. The actual physical dimensions can vary based on the specific design and technology used.

Fin Width: In FinFET (Fin Field-Effect Transistor) technology, which is commonly used in advanced nodes, the width of the fins (the vertical structures that form the channel of the transistor) may also be around the 3nm mark.

Contact and Interconnect Features: The 3nm designation can also refer to the minimum feature size for various interconnects and other elements on the chip.

Overall Density: The 3nm node indicates a significant increase in transistor density, allowing for more transistors to be packed into a given area, which can lead to improved performance and energy efficiency.

In summary, while “3nm” is a marketing term that signifies a level of technology and capability in semiconductor manufacturing, it does not correspond to a single physical measurement but rather a set of dimensions and characteristics associated with the manufacturing process and the resulting chip design.

豆包 1.5 Pro

In a 3 - nm chip, the “3 nm” originally referred to the gate length of the transistors on the chip, although it has become more of a marketing - and - technology - generation term in modern semiconductor manufacturing. Here’s a detailed explanation:

Traditional meaning: Gate length

Transistor structure and gate role

A transistor is the fundamental building block of a semiconductor chip. It consists of a source, a drain, and a gate. The gate acts as a switch that controls the flow of electrons between the source and the drain. When a voltage is applied to the gate, it allows or blocks the flow of current, enabling the binary operations (0s and 1s) that form the basis of digital computing.

The gate length is the physical distance between the source and the drain, measured along the path of electron flow under the gate. In the early days of semiconductor technology development, the gate length was a crucial parameter directly related to the performance and power consumption of transistors.

Impact of reducing gate length

Reducing the gate length to 3 nm offers several advantages. Shorter gate lengths allow electrons to travel a shorter distance between the source and the drain, which means that transistors can switch on and off more quickly. This results in higher - speed operation of the chip, enabling faster data processing and better overall performance.

Additionally, shorter gate lengths generally lead to lower power consumption. Since the electrons have less distance to travel, less energy is dissipated as heat during the switching process.

Modern interpretation

Beyond gate length

As semiconductor technology has advanced, the relationship between the named “node” (such as 3 nm) and the actual gate length has become less straightforward. Chip manufacturers now use the node number as a way to represent an overall advancement in the manufacturing process, which includes improvements in multiple aspects such as transistor architecture, materials, and patterning techniques.

For example, modern chips may use fin - field - effect transistors (FinFETs) or even more advanced transistor structures like gate - all - around (GAA) transistors. In these complex architectures, the 3 - nm designation encompasses improvements in the overall density of transistors on the chip, power efficiency, and performance, rather than simply referring to the gate length. The actual gate length may be different from 3 nm, but the overall technology generation is still labeled as 3 nm to signify its advanced nature compared to previous nodes.

浮点搜索2.0

思考了 7 秒

3nm芯片中,“3nm”这个数值并非指任何单个物理部件的精确尺寸。它是一个工艺节点的标识符,代表着芯片制造技术的进步,反映了芯片整体密度、功耗和性能的提升,而非某个特定物理尺寸[1, 3, 6]。

虽然一些资料提到3nm可能对应着晶体管中某个最小尺寸的物理特征[2, 9, 10],例如栅极长度或金属间距,但实际上并没有一个单一的、普遍接受的定义3。 不同厂商的3nm工艺,其具体的物理尺寸(例如鳍式场效应晶体管FinFET的鳍片宽度、接触多晶硅间距CPP、金属间距等)都可能有所不同[4, 5, 9]。 例如,一个所谓的“7nm”晶体管的实际尺寸可能远大于7nm,例如57x40nm4。 而且,随着技术的进步,用于衡量芯片尺寸的指标也在不断变化10。

总而言之,3nm更像是一个营销术语,代表着比前代工艺更先进的制造技术,而不是某个特定物理部件的精确尺寸1。 要精确测量3nm芯片的各个部件尺寸,需要用到诸如CD-SEM(关键尺寸扫描电子显微镜)、原子力显微镜(AFM)、透射电子显微镜(TEM)等先进的纳米级测量设备[11, 12, 15, 18],并且测量结果会因测量方法和具体部件而异。 目前,即使是最先进的测量技术,也难以达到1nm以下的精度[11, 13]。

DeepSeek-R1满血版

思考了 23 秒

In a 3nm chip process, the term “3nm” does not correspond to a specific physical dimension of any single component. Instead, it is a marketing and generational label inherited from historical naming conventions, reflecting incremental improvements in transistor density, power efficiency, and performance over previous nodes (e.g., 5nm, 7nm). Here’s a breakdown of key points:

Historical Context:

Older nodes (e.g., 90nm, 65nm) were named after the gate length (the distance between a transistor’s source and drain). This metric directly influenced performance and power.

As transistors shrank below ~30nm, the naming convention diverged from literal measurements due to complex 3D designs (e.g., FinFETs) and marketing strategies.

Modern Transistor Structures:

In FinFET or GAAFET (Gate-All-Around) transistors, features like fin width, gate length, and metal pitch are critical but not directly tied to the “3nm” label.

For example, in a 3nm node:

Gate length might be ~12–14nm (far larger than 3nm).

Fin pitch or metal interconnect pitch could be ~20–30nm.

These dimensions are scaled down from previous nodes but remain larger than the process name suggests.

Industry Dynamics:

The lack of standardization allows companies (TSMC, Samsung, Intel) to use the “3nm” label flexibly, often for competitive positioning. One foundry’s “3nm” might match another’s “5nm” in density or performance.

Advancements like EUV lithography enable finer patterning but do not anchor the node name to a specific feature.

Key Takeaway:

The “3nm” designation signifies generational progress rather than a measurable 3nm component. It reflects overall improvements in transistor density (e.g., more transistors per mm²), power efficiency, and speed compared to earlier nodes, even though no individual feature is exactly 3nm.